# RVD – 1005 VISUAL DISPLAY UNIT

## INSTRUCTION MANUAL

QUALITY COMMUNICATIONS EQUIPMENT

#### HAL RVD-1005 VISUAL DISPLAY UNIT

#### TECHNICAL MANUAL

| Ser | ia | No. |  |

|-----|----|-----|--|

|-----|----|-----|--|

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### WARRANTY

The HAL Communications RVD-1005 Visual Display Unit is fully guaranteed against defects in materials and workmanship for a period of one year. Should repair or replacement parts be required, notify HAL Communications Corp. promptly. The warranty period is measured from the date of the original invoice to the postmark date of your notification letter. Please do not return your unit to the factory for repair or adjustment until you have received a written return authorization.

HAL Communications assumes no responsibility for the repair or replacement of parts for units which have been damaged, abused, improperly installed, or modified and reserves the right to change the design of this visual display system without incurring obligation to incorporate such changes into existing units.

Copyright © 1975 by HAL Communications Corp., Urbana, Illinois. Printed in the United States of America. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of the copyright owner.

#### CONTENTS

| 1. | Introduction and Specifications              | 1-1 |

|----|----------------------------------------------|-----|

| 2. | Installation and Operating Instructions      | 2-1 |

| 3. | Theory of Operation                          | 3-1 |

| 4. | Maintenance                                  | 4-1 |

| 5. | Using a Television Set as a Monitor          | 5-1 |

| 6. | Schematic Diagrams                           | 5-1 |

| 7. | Printed Circuit Card Layouts and Photographs | 7-1 |

| 8. | Parts List                                   | 3-1 |

#### TABLES

| Table 1.1: | Display Specifications . |   |   |   |   |   |   |   |   |  |   | 1-2 |

|------------|--------------------------|---|---|---|---|---|---|---|---|--|---|-----|

| Table 1.2: | Input Specifications     |   |   | • |   |   |   | • | • |  |   | 1-5 |

| Table 1.3: | Video Specifications     | • |   |   |   | • | • |   |   |  | • | 1-6 |

| Table 1.4: | General Specifications . |   |   |   |   | • | • | • |   |  | • | 1-6 |

|            | Baudot and ASCII Codes . |   |   |   |   |   |   |   |   |  |   |     |

| Table 3.2: | Input Timing Frequencies |   |   |   | • |   | • |   |   |  |   | 3-4 |

| Table 4.1: | Voltage Measurements     |   | • |   |   |   |   |   |   |  |   | 4-2 |

#### ILLUSTRATIONS

| Figure<br>Figure<br>Figure<br>Figure                           | 1.2:                                                         | Character Display Format              | 1 - 2<br>1 - 3<br>1 - 4<br>1 - 4                                     |

|----------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------|

| Figure<br>Figure<br>Figure<br>Figure<br>Figure                 | 2.2:<br>2.3:<br>2.4:                                         | Rear Panel Connections                | 2- 2<br>2- 3<br>2- 4<br>2- 4<br>2- 6                                 |

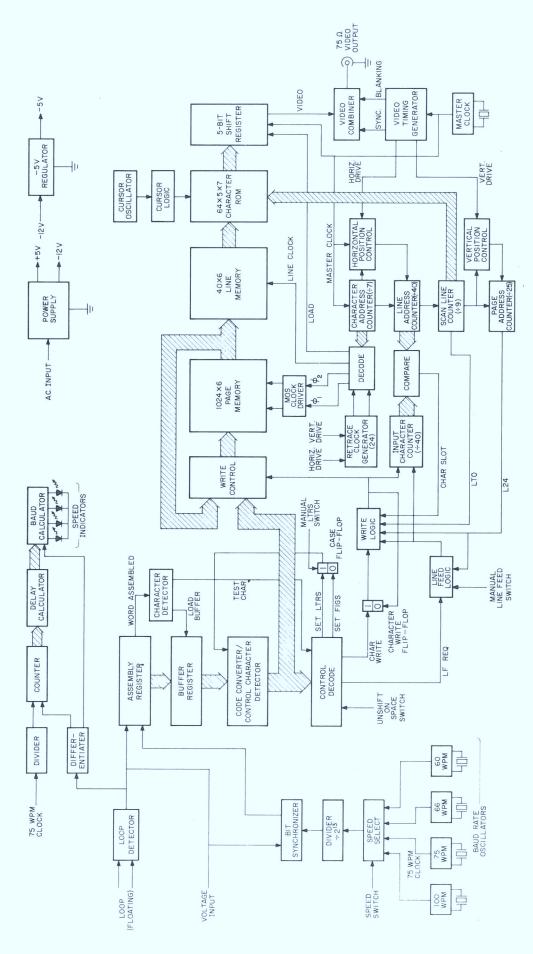

| Figure<br>Figure<br>Figure<br>Figure                           | 3.2:<br>3.3:                                                 | RVD-1005 Block Diagram                | 3- 2<br>3- 4<br>3-10<br>3-14                                         |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure       | 5.2:<br>5.3:<br>5.4:<br>5.5:                                 | Typical Transistor Video Detector     | 5- 1<br>5- 2<br>5- 2<br>5- 3<br>5- 3                                 |

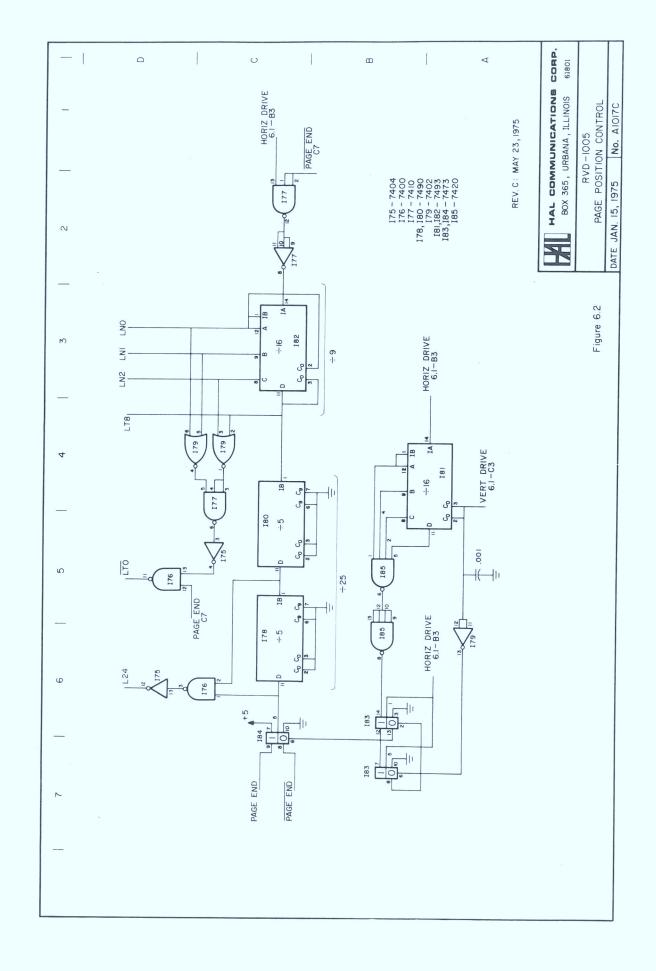

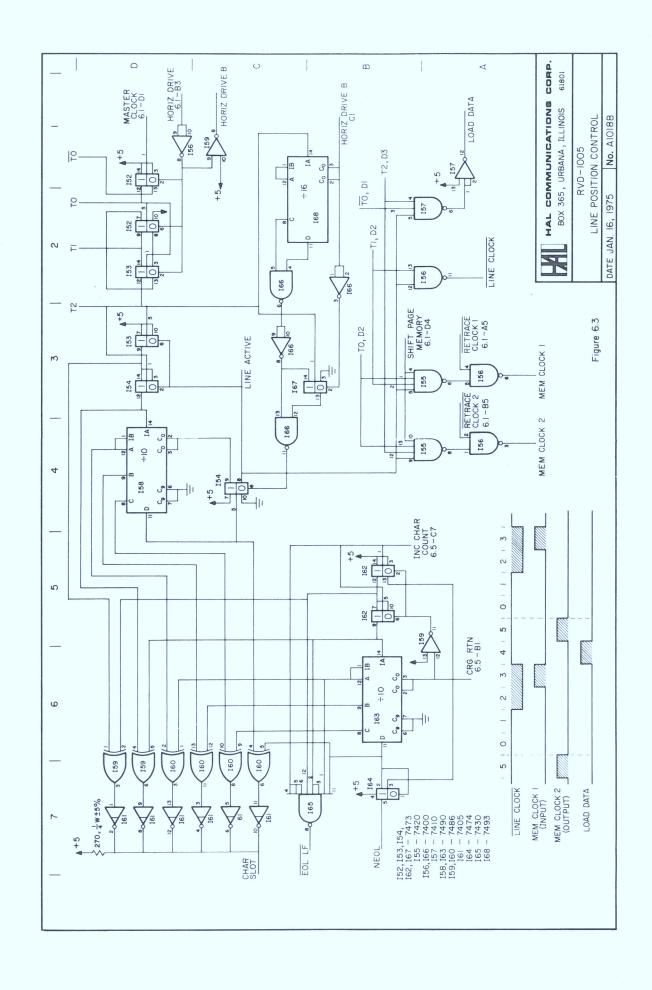

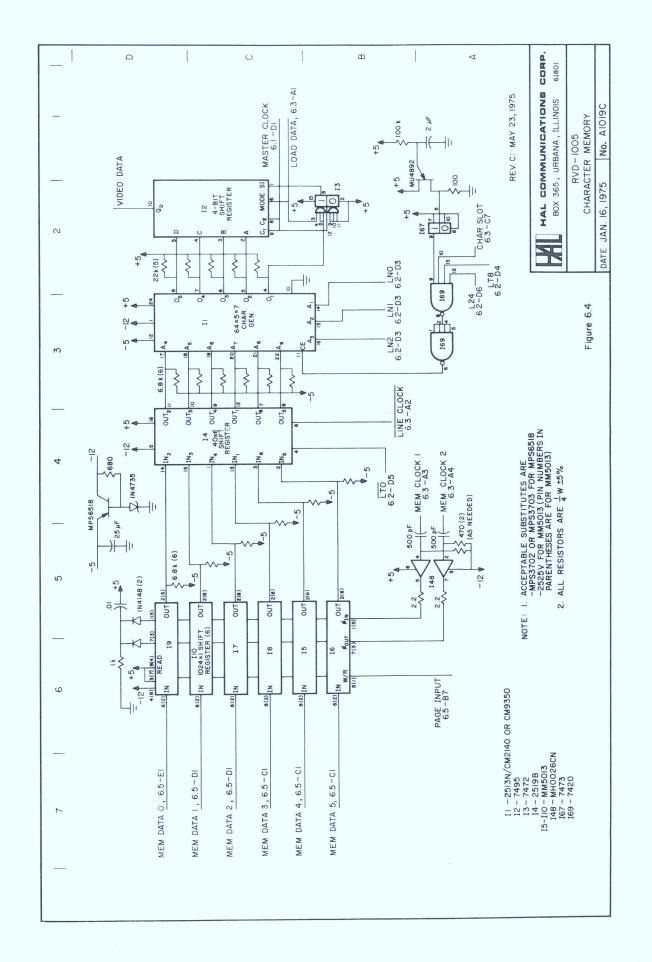

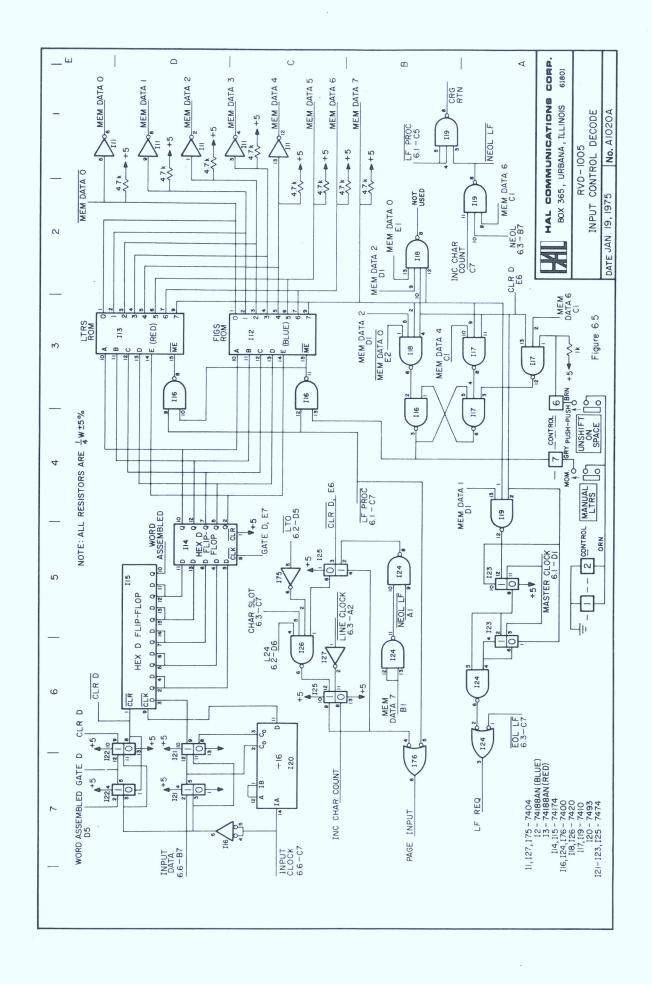

| Figure Figure Figure Figure Figure Figure Figure Figure Figure | 6.2:<br>6.3:<br>6.4:<br>6.5:<br>6.6:<br>6.7:<br>6.8:<br>6.9: | Video, Line Feed, and Retrace Control | 6- 2<br>6- 3<br>6- 4<br>6- 5<br>6- 6<br>6- 7<br>6- 8<br>6- 9<br>6-10 |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure                 | 7.2:<br>7.3:<br>7.4:                                         | Logic Circuit Board Photograph        | 7- 2<br>7- 3<br>7- 4<br>7- 5<br>7- 6                                 |

## 1. Introduction and Specifications

The HAL Communications RVD-1005 is a visual display unit designed for use in radioteletype systems. It is capable of decoding, storing, and displaying up to 1000 alphanumeric characters on the screen of a video monitor or converted television receiver. When used with a suitable demodulator (terminal unit) such as the HAL ST-5 or ST-6, it provides instantaneous, silent reception of radioteletype signals.

A successor to HAL's popular RVD-1002, the 1005 offers an improved display format, an automatic speed indicator, and input terminals for both loop and EIA-level inputs. Special circuitry has been added to prevent overprinting and the splitting of short words at the end of a line.

The RVD-1005 accepts serially transmitted character codes and generates the video signal required to display those characters on the monitor screen. The incoming characters are stored in a recirculating memory, which is used to refresh the display on every complete scan of the raster.

#### Display Characteristics

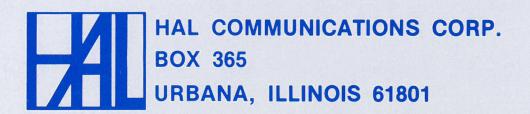

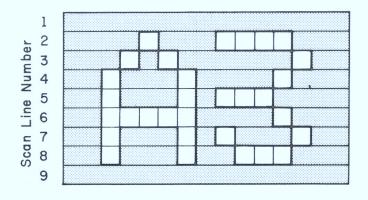

The 1000-character display "page" is divided into 25 horizontal lines of 40 characters each. Characters are produced by a pattern of bright dots on a dark field. The 35 dots in the matrix used to display each character are arranged in five vertical columns of seven dots each, as shown in Figure 1.1. The character height is equal to the space required for seven horizontal scan lines. The width is approximately five sevenths of the height. The actual size of the displayed characters depends, of course, on the size of the monitor screen. Complete display specifications are given in Table 1.1.

The first incoming characters appear on the bottom line of the display. When that line is full, all characters in it shift up one line, leaving the bottom line blank and ready to receive new characters. This line feed process recurs each time the bottom line is filled or when a line feed character is received. To prevent the splitting of short words at the end of a line, a line feed occurs automatically if a space is received after the 34th character in a line. The characters which follow the space appear at the left margin of the next line. When all 25 lines have been used, the next line feed causes the top line to be deleted.

<sup>&</sup>lt;sup>1</sup>The video monitor is not supplied with the RVD-1005. An optional monitor is available. Section 5 provides instructions for modifying a television receiver to serve as a monitor.

$<sup>^2</sup>$ In early production units with serial numbers less than 220, the line feed occurs if a space is received after the  $36\,th$  character.

Figure 1.1: Character Display Format

## TABLE 1.1 DISPLAY SPECIFICATIONS

| Character format                               | 5 x 7 dot matrix   |

|------------------------------------------------|--------------------|

| Line format                                    | 40 characters/line |

| Page format                                    | 25 lines/page      |

| Character width-to-space ratio                 | 5:2                |

| Character-plus-space time <sup>1</sup>         | 875 nanoseconds    |

| Line height-to-space ratio                     | 7:2                |

| Horizontal scan lines per character line       | 7                  |

| Horizontal scan lines per intercharacter space | 2                  |

| Horizontal line display percent <sup>2</sup>   | 83 percent         |

| Vertical field display percent <sup>3</sup>    | 78 percent         |

<sup>&</sup>lt;sup>1</sup>Defined as the time required during a horizontal scan to display one character plus an intercharacter space.

$<sup>^2</sup>$  Defined as the percentage of the horizontal line used in displaying 40 characters and the spaces between them.

<sup>&</sup>lt;sup>3</sup>Defined as the percentage of the vertical field used in displaying 25 character lines and the interline spaces.

#### Input Characteristics

The display unit inputs accept serially transmitted, five-level, Baudot-coded characters, the standard for radioteletype and many other types of data transmission. The unit operates at all standard speeds--60, 66, 75, and 100 words per minute.

Two separate input jacks are provided. One accepts voltage inputs and is designed to be compatible with EIA standard voltage levels. A current input is also provided and can be used to connect the system in series with the station loop circuit. Complete input specifications appear in Table 1.2.

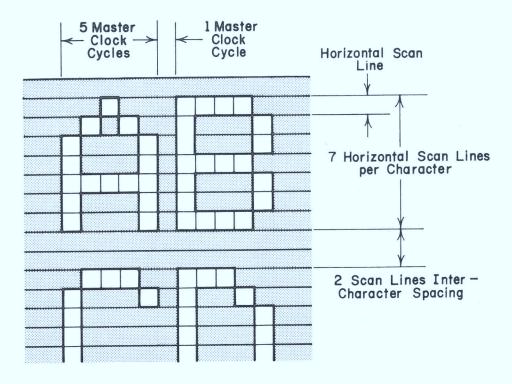

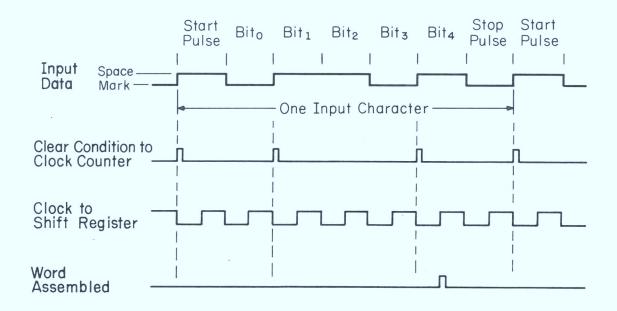

Figure 1.2 shows the format of the input code. The code for a particular character consists of a start pulse, five data pulses, and a stop pulse. Each pulse may represent either a "mark" or a "space." In terms of the voltage input, space pulses are positive; mark pulses are negative. For the loop circuit input, mark pulses are represented by the flow of current. During space pulses, the current is interrupted.

Figure 1.2: Format of Typical Input Character

The start pulse for any character is a space. Data pulses 0 through 4 follow the start pulse and may be either marks or spaces, depending on the character being received. The stop pulse is a mark. All pulses are of equal length except the stop pulse, which may be longer than the others. The pulse length varies with the operating speed, as indicated in Table 1.2.

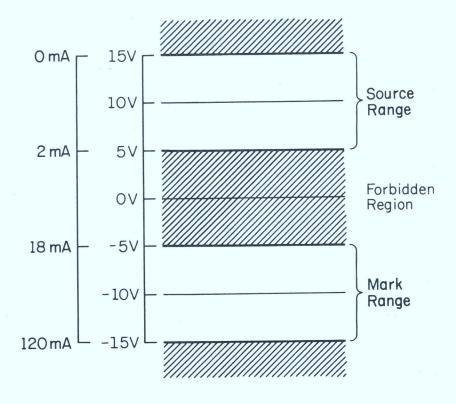

As Figure 1.3 illustrates, the input mark and space pulses must fall within a certain voltage or current range to produce valid copy. For the voltage input, space pulses must be in the range from +5 to +15 volts. Mark pulses must lie between -5 and -15 volts. When the current input is used, the loop current must be in the range from 18 to 120 mA for mark pulses and less than 2 mA for spaces. Pulses which fall in the forbidden current or voltage ranges may cause uncertainty or errors in the display.

Figure 1.3 Input Limits

Figure 1.4 Video Output Format

## TABLE 1.2 INPUT SPECIFICATIONS

| Input data form:                                                                            | Serial                                                                                  |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Word format Pulse 1: Pulse 2: Pulse 3: Pulse 4: Pulse 5: Pulse 6: Pulse 7:                  | Start pulse Data pulse 0 Data pulse 1 Data pulse 2 Data pulse 3 Data pulse 4 Stop pulse |

| Select pulse length<br>60 WPM:<br>66 WPM:<br>75 WPM:<br>100 WPM:                            | 22 milliseconds 20 milliseconds 17.57 milliseconds 13.47 milliseconds                   |

| Start pulse length:<br>Data pulse length:<br>Stop pulse length:                             | Same as select pulse<br>Same as select pulse<br>Greater than or equal to select pulse   |

| Voltage input characteristics<br>Mark voltage:<br>Space voltage:<br>Input impedance:        | -5 to -15 volts<br>+5 to +15 volts<br>120 ohms or greater                               |

| Loop (current) input Mark current: Space current: Input impedance: Isolation, loop to case: | 18 to 120 mA<br>2 mA or less<br>20 ohms or less<br>10 megohms or greater                |

#### Output Characteristics

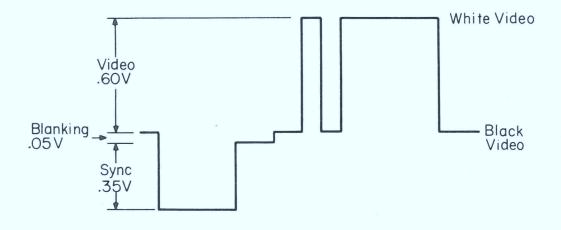

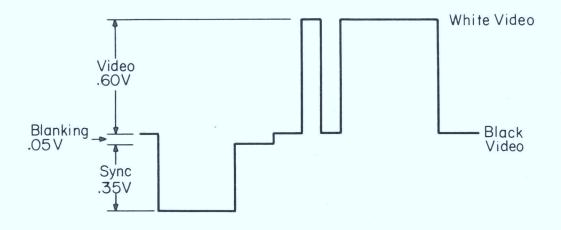

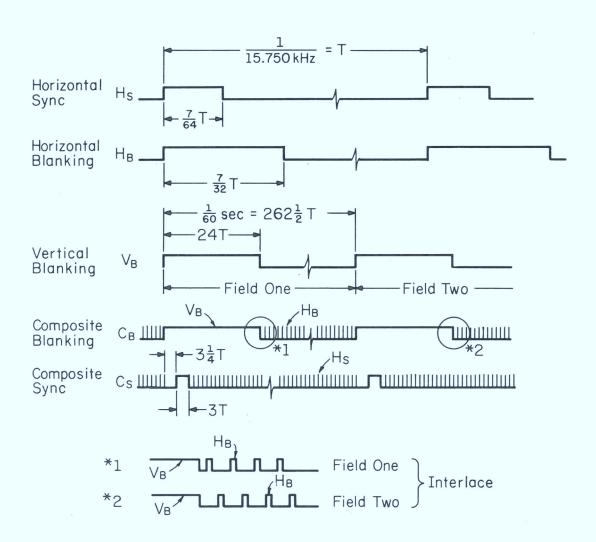

The output video signal is compatible with EIA RS-170, 525-line-per-frame television systems, standard in the United States. Table 1.3 lists the video output specifications; the waveform is shown in Figure 1.4. Detailed instructions for connecting the RVD-1005 video output to a television receiver are given in Section 5.

#### Construction and Physical Specifications

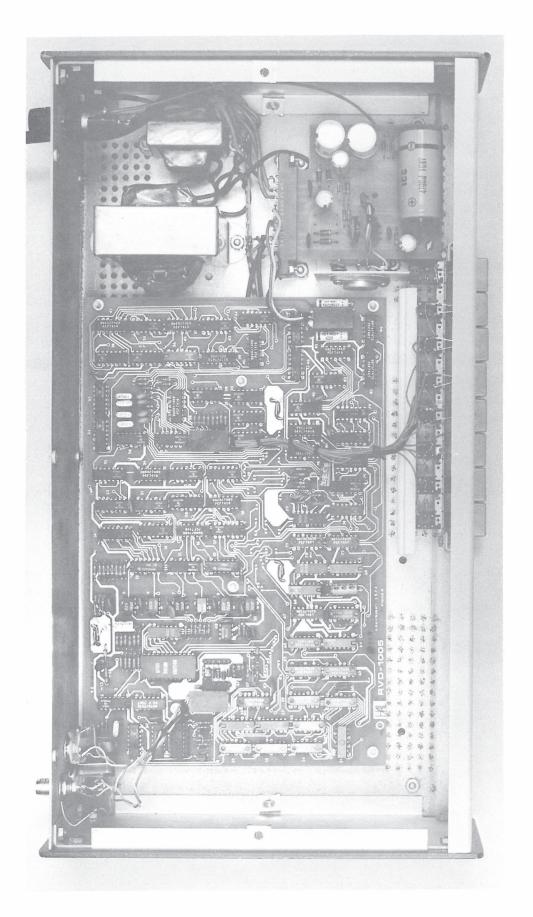

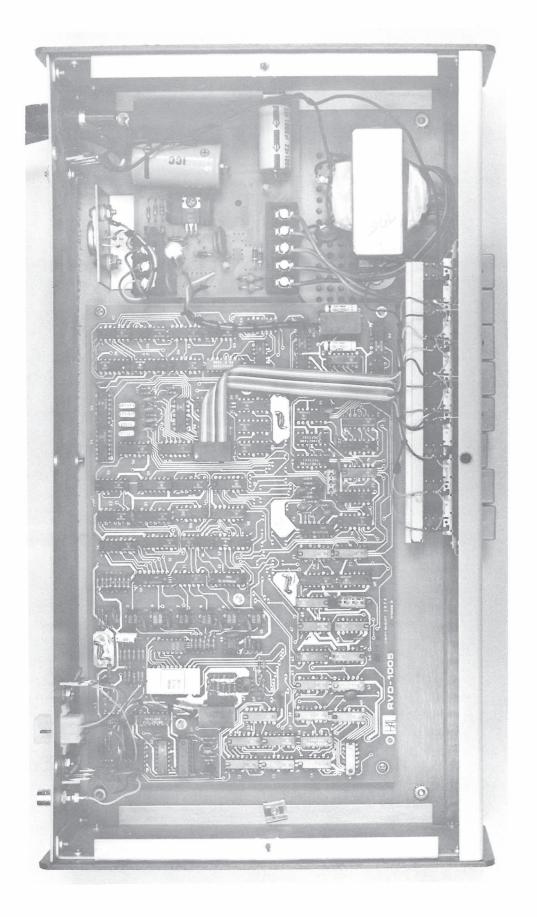

The RVD-1005 circuitry is constructed on two printed circuit boards. The logic and signal-processing circuitry occupies the larger of these boards. The power supply components are mounted on the smaller one. They are housed in an attractive two-tone grey cabinet. A rack-mounting model, the RVD-1005R, is designed for installation in a standard 19-inch relay rack. Size, weight, temperature, and input power specifications are given in Table 1.4.

Figure 1.3 Input Limits

Figure 1.4 Video Output Format

## TABLE 1.2 INPUT SPECIFICATIONS

| Input data form:                                                                            | Serial                                                                                  |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Word format Pulse 1: Pulse 2: Pulse 3: Pulse 4: Pulse 5: Pulse 6: Pulse 7:                  | Start pulse Data pulse 0 Data pulse 1 Data pulse 2 Data pulse 3 Data pulse 4 Stop pulse |

| Select pulse length<br>60 WPM:<br>66 WPM:<br>75 WPM:<br>100 WPM:                            | 22 milliseconds 20 milliseconds 17.57 milliseconds 13.47 milliseconds                   |

| Start pulse length:<br>Data pulse length:<br>Stop pulse length:                             | Same as select pulse<br>Same as select pulse<br>Greater than or equal to select pulse   |

| Voltage input characteristics Mark voltage: Space voltage: Input impedance:                 | -5 to -15 volts<br>+5 to +15 volts<br>120 ohms or greater                               |

| Loop (current) input Mark current: Space current: Input impedance: Isolation, loop to case: | 18 to 120 mA<br>2 mA or less<br>20 ohms or less<br>10 megohms or greater                |

#### Output Characteristics

The output video signal is compatible with EIA RS-170, 525-line-per-frame television systems, standard in the United States. Table 1.3 lists the video output specifications; the waveform is shown in Figure 1.4. Detailed instructions for connecting the RVD-1005 video output to a television receiver are given in Section 5.

#### Construction and Physical Specifications

The RVD-1005 circuitry is constructed on two printed circuit boards. The logic and signal-processing circuitry occupies the larger of these boards. The power supply components are mounted on the smaller one. They are housed in an attractive two-tone grey cabinet. A rack-mounting model, the RVD-1005R, is designed for installation in a standard 19-inch relay rack. Size, weight, temperature, and input power specifications are given in Table 1.4.

#### Accessories

The RVD-1005 is supplied with the following accessories:

Four-foot video cable with male BNC connector at each end Two four-foot two-conductor shielded cables Two input connector shells (male) 12 connector pins (female) One manual

#### TABLE 1.3

#### VIDEO SPECIFICATIONS

| Lines per field:                | 262.5                    |

|---------------------------------|--------------------------|

| Fields per frame:               | 2                        |

| Lines per frame:                | 525                      |

| Line rate:                      | 15.750 KHz               |

| Field rate: <sup>1</sup>        | 60 Hz                    |

| Timing tolerance:               | ±0.1%                    |

| Synchronization voltage:        | 0.35 volt peak-to-peak   |

| Synchronization polarity:       | negative                 |

| Video voltage: <sup>2</sup>     | 0.60 volt peak-to-peak   |

| Composite video signal voltage: | 1.0 volt peak-to-peak    |

| Voltage tolerance:              | ±10% with specified load |

| Peak video bandwidth: 3         | 3.1 MHz                  |

| Load impedance:                 | 75 ohms ±5%              |

<sup>1</sup>Fields are automatically interlaced.

$^2\mathrm{Figure}$  1.4 shows the proper video output waveform.

<sup>3</sup>Defined as the frequency above which all energy could be eliminated with no degradation of picture quality. Readability decreases noticeably when energy below 3.1 MHz is eliminated.

## TABLE 1.4 GENERAL SPECIFICATIONS

| Size:                  | RVD-1005                 | 3.5" H, 17" W, 9" D<br>(8,9 x 43,2 x 22,9 cm)              |

|------------------------|--------------------------|------------------------------------------------------------|

|                        | RVD-1005R                | 3.5" H, 19" W, 9" D<br>(8,9 x 48,3 x 22,9 cm)              |

| Weight:                | 7.5 pounds               | (3,4 kilograms)                                            |

| Shipping weight:       |                          | (6,4 kilograms)                                            |

| Operating temperature: | 65 to 80°                | F (18.3 to 26.7°C)                                         |

| Power requirements:    | 105 to 125<br>210 to 250 | v AC, 50 to 60 Hz, 25 watts<br>v AC, 50 to 60 Hz, 25 watts |

### 2. Installation and Operating Instructions

#### Installation

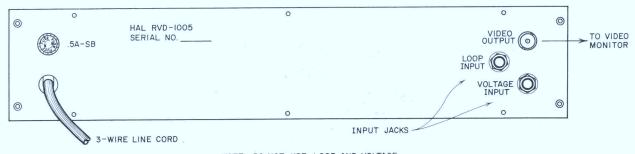

The RVD-1005 is very simple to install. The first step is to connect the video output to an external video monitor. A four-foot cable with BNC connectors at each end is supplied for this purpose. Connect one end of the cable to the rear-panel jack labelled VIDEO OUTPUT, as shown in Figure 2.1. Connect the other end to the video input jack of your monitor.

NOTE: The video output line must be terminated by a 75-ohm impedance. Check the monitor specifications to determine whether its input represents a 75-ohm load. The load need not provide a DC return path.

You may easily modify a standard television receiver for use as a video monitor. Full details are given in Section 5 of this manual.  $\underline{\text{DO NOT}}$  use a television set in which one side of the AC power line is connected directly to the chassis or to the ground return for the circuitry unless you supply AC power to the set from a reliable isolation transformer.

Two inputs are provided. One is a voltage input which may be driven by an output from your terminal unit (demodulator), provided that the mark and space voltage levels fall within the range indicated in Figure 1.3. If you prefer, or if an output of the required voltage level is not available on your terminal unit, you may connect the RVD-1005 in series with other equipment in your DC printer loop circuit by using the LOOP input connections. Break the station loop and connect the two cable conductors in series with the other equipment. The polarity is not important.

If you plan to drive the RVD-1005 input from a HAL ST-5 or ST-6 terminal unit, the voltage input may be connected directly to the FSK jack of the terminal unit. For other demodulators, check the voltage levels carefully before connecting the signal to the visual display unit input.

NOTE: The two inputs (VOLTAGE INPUT and LOOP) may not be used simultaneously. Make connections to one or the other but not both.

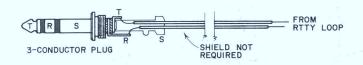

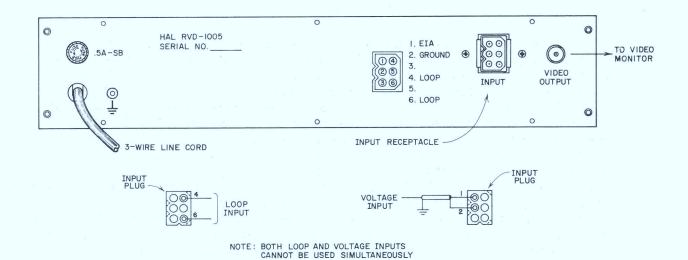

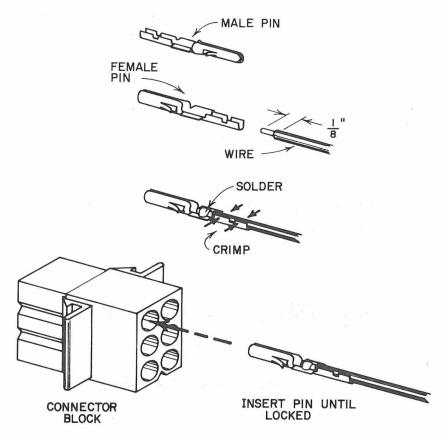

A six-pin connector on the rear panel of the RVD-1005 can be wired for either voltage or current (loop) inputs. The correct connections are shown in Figure 2.1. Attach the pins to the wires as shown in Figure 2.2 and insert the pins in the locations indicated in Figure 2.1. Once inserted in the shell, the pins are not easily removed. Sufficient pins and two plug shells are provided so that cables for both loop and voltage inputs can be prepared.

NOTE: DO NOT USE LOOP AND VOLTAGE INPUTS SIMULTANEOUSLY

a. RVD-1005 Serial Number Less Than 346

b. RVD-1005 Serial Number 346 and Higher

Figure 2.1 Rear Panel Connections

Figure 2.2 Preparation of Input Connector

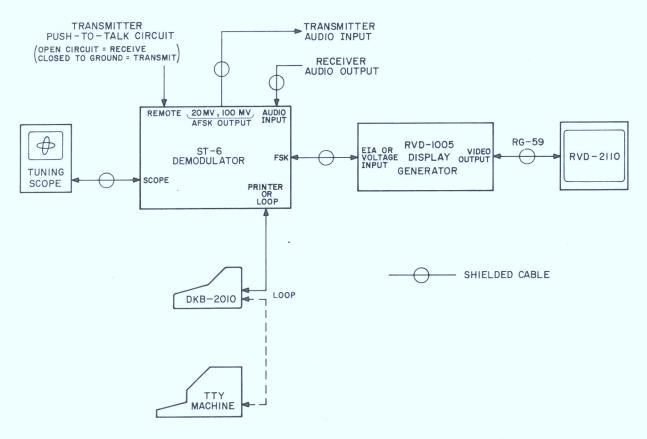

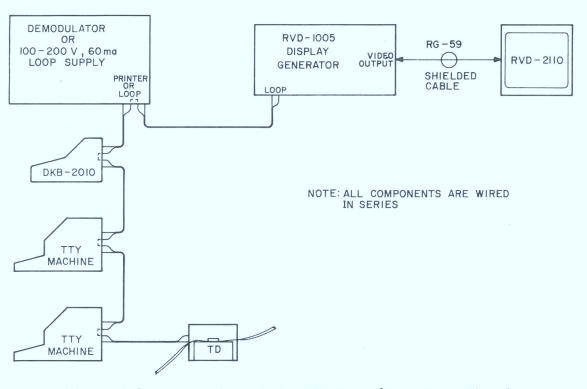

Two slightly different ways in which the RVD-1005 can be connected to a teletype system are shown in Figures 2.3 and 2.4. The use of the FSK data output connection of the ST-6 (or ST-5) to drive the RVD is shown in Figure 2.3. As noted, shielded cables should be used between the ST-6 and the RVD as well as for the video connection, scope connection, and audio input and output connections. The connections to the DKB-2010 and TTY machine can be made with twin parallel-conductor cable ("zip-cord") or other two-conductor cable. The shielded cables should be as short as possible for a given installation but may be as long as six feet or more if necessary. Longer cable lengths may result in problems with RF interference or ground loops. In all cases, the cabinets of all parts of the system should be positively connected together with 18 gauge wire or 1/4" wide shieldbraid to assure good ground connections. DO NOT rely upon the power cord safety grounds or the shield of shielded signal cables to provide a RF groundreturn path. Figure 2.4 illustrates how the RVD-1005 may be connected in a standard 60 ma series TTY loop circuit. None of the loop connections need be shielded, but all equipment cabinets should be bonded together. The ST-6 (or ST-5) may also be connected in this manner, if desired. Be sure that connections are made to the proper input pins of the RVD input connector and that the voltages and currents are compatible with the limits shown in Figure 1.3 and Table 1.2.

Figure 2.3 Connection of the RVD with the ST-6

Figure 2.4 Connection of the RVD in a 60 ma Loop Circuit

Check the input voltage specification for your unit. It is designed for 115 volt, 50 to 60 Hz operation unless otherwise requested on your order. Units equipped for operation from nominal 230 volt, 50 to 60 Hz power sources are identified by a label on the rear panel and a tag on the power cord.

Connect the AC cord to a power source of the proper voltage and frequency. Use only a *three-wire grounding AC outlet* to protect the operator from electrical shock and to minimize interference from stray RF fields.

When mounting your unit, check that the ventilation holes in the top and bottom covers are not obstructed. Avoid mounting it above units which generate heat.

#### Operation

The RVD-1005 is as simple to operate as it is to install. The eight pushbuttons on the front panel, shown in Figure 2.5, control all functions.

Provide an input signal by tuning to a RTTY station. Choose a signal that is relatively noise free and, if possible, of known speed. Check that the terminal unit is demodulating the signal properly. If you have connected your display unit into the station loop circuit rather than to the terminal unit, you may prefer to generate an input signal by typing on your keyboard or by running a paper tape on a tape reader connected into the loop.

Switch on the AC power to the video monitor or television receiver. Press any of the speed selector buttons to switch the visual display system on. With the test signal applied, observe the speed indicator lights located directly above the speed selector buttons. The one corresponding to the speed (in words per minute) of the input signal should light. Press the speed button directly below the light to set the RVD-1005 to the correct operating speed. Characters should start to appear on the monitor screen.

The speed may be changed at any time by pressing one of the other speed selector buttons. Note that the speed lights simply *indicate* the speed of the incoming signal; they do not set the unit's operating speed. That function is always performed manually by the operator, using the speed selector buttons.

The speed indicator lights give an *estimate* of the speed of the received signal. They may provide an incorrect indication if the input signal is noisy, if its speed is significantly different from the display unit's four standard operating speeds, or if the received signal has significant bias distortion (difference between the durations of mark and space pulses).

The UNSHIFT ON SPACE button, located to the left of the four speed selectors, activates the automatic letters-shift circuitry, which causes the display to return to letters case every time a space character is received. This feature prevents the system from erroneously displaying figures-case characters instead of letters if a letters-shift command is not received at the proper time. Press the button once to enable this feature; press it again to return to normal operation.

If you wish to manually return the system to letters case, press the MANUAL LTRS button momentarily. A letters-shift command will be produced, shifting the display to letters case and overriding any casecontrol characters received while the button is pressed.

Similarly, the MANUAL LF button produces a linefeed command when it is pressed, causing all characters in the display to jump up one line and leaving the bottom line blank. The button overrides the input signal while it is depressed. Whenever a linefeed occurs, whether it is received in the input character stream or produced manually by pressing the button, a carriage return automatically occurs so that the next character will appear at the left margin.

Whenever a 40-character line has been filled, the unit causes a linefeed and carriage return to occur, so that the next character received will appear at the left margin of a new line. In addition, the linefeed and carriage return are automatically produced if a space is received after the 34th character in a line. This feature prevents the splitting of words which start near the end of a line.

When you have finished using the display unit, remove AC power by pressing the POWER button located to the right of the speed selectors.

| LINE<br>FEED | LTRS | UNSHIFT<br>ON<br>SPACE | 60 (45) | 66(50) | 75(57) | D) ———————————————————————————————————— | POWER |

|--------------|------|------------------------|---------|--------|--------|-----------------------------------------|-------|

|              |      |                        | a.      |        |        |                                         |       |

Figure 2.5 Front Panel Controls

### 3. Theory of Operation

#### Basic Operating Principles

The RVD-1005 circuitry is composed of two main parts: (1) the input section, and (2) the memory and display section. A block diagram is shown in Figure 3.1. The input section accepts each character in sequence from the local loop or terminal unit, converts it from serial to parallel form and then from Baudot to a modified ASCII³ code, checks it to determine whether it is a printing character or a control code (such as a line feed or carriage return), and stores it until the main memory is ready to accept it.

The memory and display section stores the incoming characters and maintains the display by continuously reading out the memory contents, generating the dot pattern required for each character, and producing the composite video signal fed to the monitor.

#### Teleprinter Code

In the standard Baudot code used in five-level teleprinter systems, each character is made up of seven sequential "select" pulses, as shown in Figure 3.2. Pulses may have either of two states; in the "mark" state, current flows in the printer loop, while in the "space" state it does not. The rest condition, when no characters are being transmitted, is always a mark.

In any character the first pulse, called the start pulse, is a space; it prepares the printer to accept the six succeeding pulses of that character. The five pulses which follow define the individual character. There is a unique pattern of these pulses for each character. The last pulse, called the stop pulse, is always a mark. It allows the printer to recover and prepare for the next character. All pulses are of equal length except for the stop pulse, which may be longer. The pulse length decreases with increased operating speed, as indicated in Table 1.2.

<sup>&</sup>lt;sup>3</sup>ASCII denotes the American Standard Code for Information Interchange, widely used in data processing systems. Table 3.1 lists the Baudot codes and their ASCII equivalents for each character.

Figure 3.1 RVD-1005 Block Diagram

| ASCII Code <sup>4</sup> | Bit Number<br>65 4321                | 00 0001<br>00 0010<br>00 0011<br>00 0100<br>00 0101                                                                         | 00 0110<br>00 0111<br>00 1000<br>00 1001<br>00 1010 | 00 1011<br>00 1100<br>00 1101<br>00 1110                                                    | 01 0000<br>01 0001<br>01 0010<br>01 0011 | 01 0101<br>01 0110<br>01 0110<br>01 1000<br>01 1001<br>01 1010 | 11 0000<br>11 0001<br>11 0010<br>11 0011 |

|-------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------|------------------------------------------|

| de                      | Case <sup>3</sup>                    |                                                                                                                             |                                                     | بالانتا                                                                                     |                                          |                                                                | L L L L L                                |

| Baudot Code             | Bit Number <sup>2</sup><br>5 4 3 2 1 | 0 0 0 1 1 0 0 1 0 0 1 1 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0             | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 1 1 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 01010                                    | 001110101101101101101110111011110111101111                     | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0  |

|                         | Character <sup>1</sup>               | K & O O B                                                                                                                   | <b>よのエー</b> つ                                       | X J Z Z O                                                                                   | <b>で</b> ぬれる⊢                            | NXXECO                                                         | 43778                                    |

ASCII Code<sup>4</sup>

Bit Number

65 4321

Baudot Code

Case<sup>3</sup>

Character<sup>1</sup>

1000

0111 1100 0001 1010

0-0

-0-00-

000---

000000

0 -

1 0 -

00000

1101

1000

1001

00000

--00-

-00-0

-000-

ショ ~ 非 ~

0--

0110

1111

00000

14 14 14 14 I

00-0-

-00-0

-0

; BELL<sup>5</sup>

0

w

1011

1010

2000

000--

0-0--

0000-

000--

BLANK<sup>6</sup> LF<sup>6</sup> CR<sup>6</sup> FIGS<sup>6</sup> LTRS<sup>6</sup>

00-

0000

10

L,F

0

0

\_

0

C

SPACE

0101

L L L L L

00--0

0---0

0000-

--00-

59780

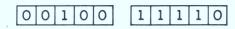

<sup>4</sup>The six least significant bits are used for character recognition in the RVD-1005A. The seventh bit is used to indicate a space code for the unshift-on-space function and the eighth bit indicates control characters. In all cases, bits I through 5 are inverted in the RVD so that the space code generated is 1111 1111, allowing insertion of spaces for the line feed function. The logic levels are negative true; that is, a ''0' is represented by a voltage level between +2.4 and +5.0 volts, a ''1' by a level between 0 and +0.8 volts.

$^5\mathrm{A}$   $^{\prime\prime}\mathrm{*}^{\prime\prime}$  is printed on the screen for the BELL function.

$^2\mathrm{Bit}$  number 1, the least significant bit, is transmitted first in the sequence of pulses. A "1" denotes a mark pulse; a "0" denotes a space.

<sup>1</sup>LF denotes line feed. CR denotes carriage return. <sup>3</sup>L denotes letters (LTRS) case. F denotes figures (FIGS) case.

$^6\mathrm{The}$  ROM does not generate true ASCII code for these control functions; only unique codes that can be recognized internally by the RVD input section.

## Table 3.1

## Baudot and ASCII Codes

Figure 3.2 Input Character Waveform

#### INPUT SECTION

The input section accepts the incoming pulses for each character and stores the first six pulses (the start pulse and the five that define the character) in a shift register. The pulses, or "bits", which have been received in serial form—that is, sequentially—are then all available simultaneously at the outputs of the shift register's six stages. That is, they have been converted to parallel form, or "assembled."

The five character-defining bits from the register outputs are fed to a buffer storage register and then to the address inputs of two read-only memories (ROM's) which convert the bit pattern to the standard ASCII code for the character. This ASCII code appears at the ROM outputs, ready for transfer to the page memory circuits in the memory and display section at the appropriate time during the memory cycle.

The input section operates independently from the memory and display section, interacting with it only when a character has been assembled and is ready to be transferred. The input section comprises these circuit functions:

- Input timing chain (oscillators, speed selector, and divider);

- 2. Bit synchronizer;

- 3. Assembly register and character detector;

- 4. Buffer register;

- Baudot-to-ASCII ROM code convertors;

- 6. Control decoder and case flip-flop;

- 7. Write command flip-flop;

- 8. Baud rate estimator.

#### Input Timing Chain

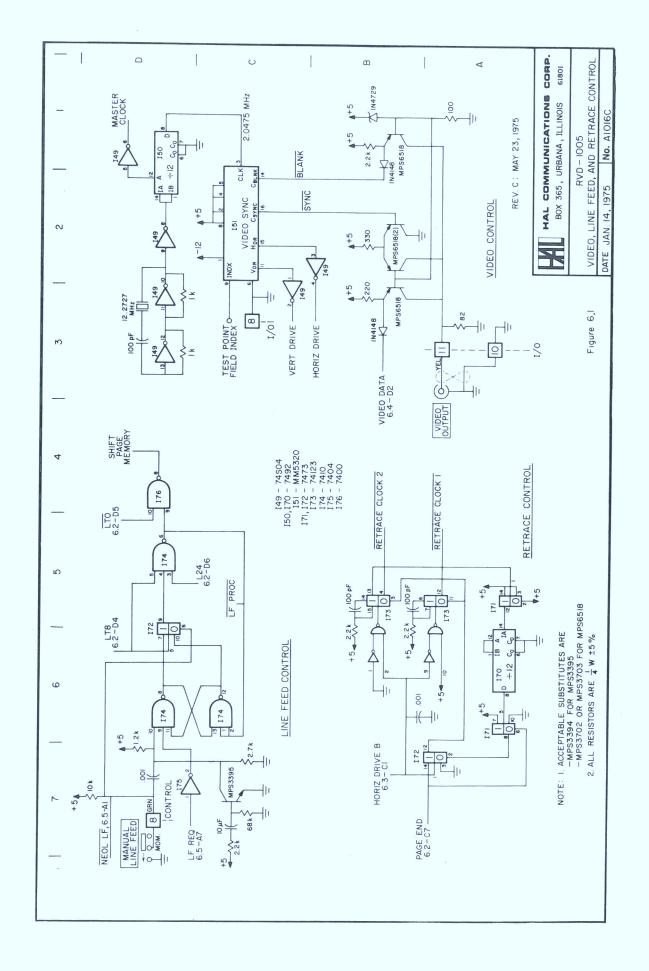

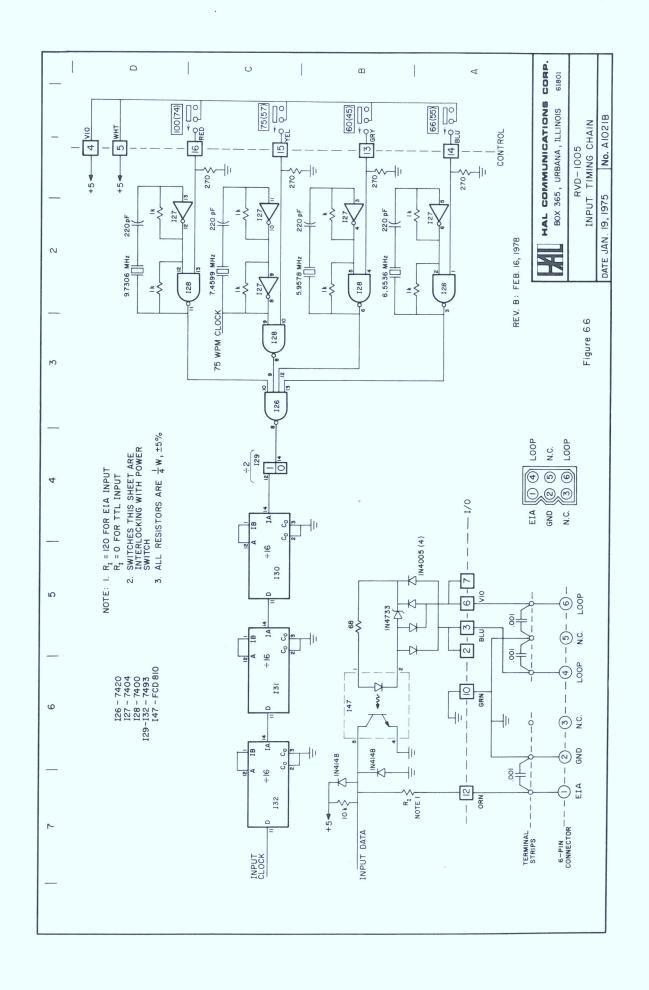

The operation of the input circuitry is synchronized with the speed of the incoming teletype signal by the input timing circuitry, shown in Figure 6.6. Four oscillators, one for each of the unit's four operating speeds, are provided. Each runs at a speed  $2^{17}$  times the baud rate of the corresponding operating speed.

The unit's operating speed is determined by depressing one of four switches, activating the appropriate oscillator. The oscillator output is divided by a factor of  $2^{13}$  (8,192) in a string of binary dividers to drive the *input clock* bus. The speeds and the corresponding frequencies are given in the following table.

Table 3.2

Input Timing Frequencies

| Speed              | Baud  | Select Pulse  | Oscillator Frequency |

|--------------------|-------|---------------|----------------------|

| (words per minute) | Rate  | Length (msec) | (MHz ± 0.1%)         |

| <b>60</b>          | 45.45 | 22            | 5.9578               |

| 66                 | 50.0  | 20            | 6.5536               |

| 75                 | 56.9  | 17.57         | 7.4599               |

| 100                | 74.2  | 13.47         | 9.7306               |

#### Input Conditioning Circuitry

For voltage inputs, no signal conditioning is necessary. The input data signal from the RTTY demodulator is coupled directly to the  $input\ data$  line, which drives the first flip-flop of the bit synchronizer (IC-21). If, however, the current input is used to connect the visual display unit into the station loop circuit, it is necessary to convert the current to a voltage signal of the appropriate level. As shown in Figure 6.6, the current passes through a bridge rectifier which makes the input circuit insensitive to the polarity of current flow through the external loop circuit. The rectifier drives a light-emitting diode in an optical isolator. The diode's light output is detected by a light-sensitive transistor which forms part of the isolator. The desired voltage output is taken from the collector of the transistor to drive the  $input\ data$  line.

#### Bit Synchronizer, Assembly Register, and Buffer Register

The input signal is fed to the inputs of the assembly register and the bit synchronizer (consisting of IC's 20 and 21), as shown in Figure 6.5. The divide-by-16 counter is driven by the input clock signal, which supplies 16 clock pulses during the duration of each select pulse at the operating speed chosen. When the circuit is inactive (when no characters are being received and the input is resting in the mark state), the divide-by-16 counter is allowed to free run. When a space pulse is received, however, indicating the beginning of a character, the mark-to-space transition resets the counter to zero on the next clock pulse.

Eight clock pulses later (in the middle of the select pulse), the output (D) stage of the counter switches from the O to the I state, shifting the assembly register one stage. The counter continues its cycle, shifting the register once every 16 clock pulses until a new mark-to-space transition is received. Thus, each select pulse is sampled in the middle of its duration and entered in the register, and the register is resynchronized at the beginning of each character and also at every mark-to-space transition within a character.

The character detector determines when the start pulse has reached the last stage of the assembly register. At that point, the six stages of the register contain the start bit and all five of the select bits which define the character. The character detector then generates a command which allows these bits to enter the buffer register, where they are stored while the character is transferred to the page memory. At the same time, the assembly register is reset and is then ready to receive the next incoming character.

#### Code Convertor and Control Character Detector

The outputs of the buffer register carry the stored character code to the inputs of the ROM code convertor and control character detector. The Baudot bit pattern for each character addresses a unique memory location in the code convertor. Each memory location stores the ASCII code equivalent of the Baudot code which constitutes that location's address. Thus, the ASCII code for the character appears at the ROM output.

As may be seen in the schematic diagram [Figure 6.6], the code convertor actually consists of two ROM's with inputs and outputs tied in parallel. One ROM stores the ASCII codes for letters-case Baudot characters; the other stores the codes for figures-case characters. Only one ROM is active at any time. The one chosen is determined by the state of the case flip-flop. In normal letters-case operation, the case flip-flop is in the set condition. Its output activates the letters ROM; the figures ROM is disabled. When a figures-shift character is received, the flip-flop changes states, activating the figures ROM and disabling the letters ROM. Thus, the correct ASCII code is produced for any character, whether in figures or letters case. The state of the case flip-flop can also be changed manually by the "manual letters" pushbutton or by the "unshift-on-space" feature (if activated), which returns the unit to letters case whenever a space is received.

There are five control characters in the normal Baudot character set: line feed (LF), carriage return (CR), letters shift (LTRS), figures shift (FIGS), and blank. These characters do not print on the screen, so they need not be entered in the page memory. The control decoder section contains circuitry which recognizes these control characters and instructs the logic circuit how to handle them.

The ROM code convertors are programmed so that the seventh bit is activated only when one of these control characters is received. This seventh bit is used to prevent the transfer of these characters to the page memory.

Logic gates decode the letters- and figures-shift characters and drive the case flip-flop. As described above, the state of this flip-flop determines which of the two code convertor ROM's is activated. In the standard RVD-1005, the carriage return function is generated in the memory and display section, since the length of the display line (40 characters) does not correspond to the standard 72-character RTTY line. Incoming carriage returns are therefore ignored. Each time a line feed occurs, the next incoming character is automatically written in the first position of the new line at the left margin.

Line feeds are decoded and drive the  $line\ feed\ request\ (LF\ REQ)$  bus, signalling the line feed logic in the memory and display section to initiate a new display line.

Space characters are also detected, even though they do appear on the display. If a space occurs after the 34th character in a line, as indicated by the state of the input character counter in the memory and display section, a logic circuit generates a line feed command so that the next character will begin a new display line.

Once an incoming character has been assembled, stored in the buffer register, and converted to ASCII code, it is ready for transfer to the memory and display section. If the stored character is not a control code, the control decode circuitry issues a command on the *character write* line to set the character write flip-flop. Its output, fed to the write logic circuitry, indicates that a character awaits transfer to the page memory. At the appropriate instant in the page memory cycle, the data bits are fed in parallel to the memory. At the instant that the character position to be written is displayed on the screen (presently it is a space) the new character is written into the page memory. The time between the "character write" signal and the actual writing of the character varies from zero to 16.67 ms which is the vertical cycle of the display. In the meantime, assembly of a new character can begin in the assembly register.

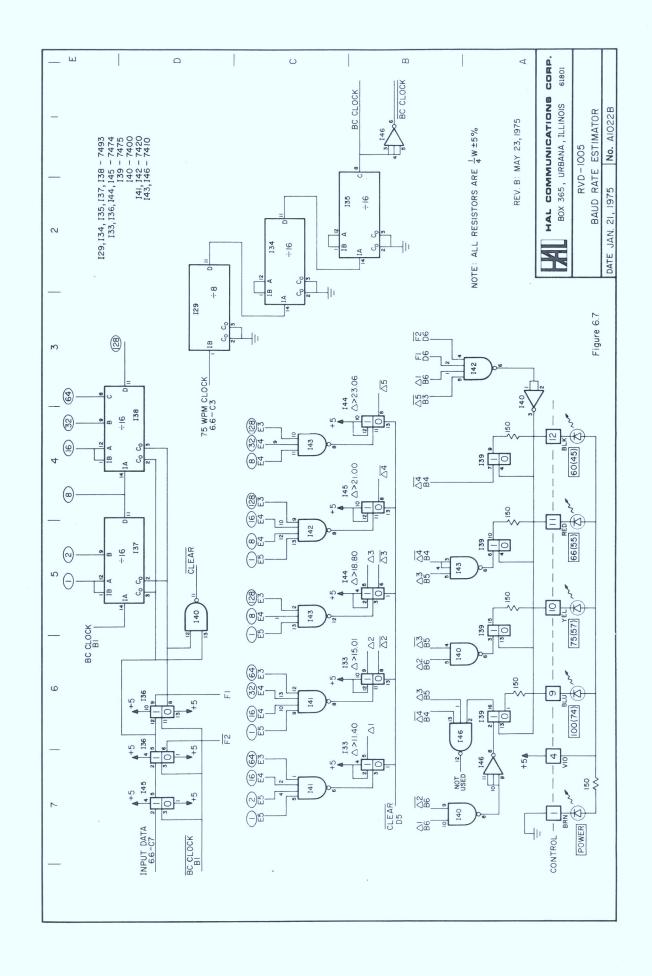

#### Baud Rate Estimator

As an aid to determining the operating speed of the incoming signal, a circuit is included which indicates the signal's baud rate. The input data signal is fed to a differentiator (composed of three flip-flops) which generates an output pulse for each mark-to-space and space-to-mark transition. These pulses control a counter, the input of which is driven by a clock signal derived from the 75 WPM clock oscillator through a frequency divider. When the space-to-mark transition occurs at the beginning of a select pulse, the counter is cleared and allowed to count the clock pulses.

As shown in the schematic diagram, Figure 6.7, logic gates are connected to the counter outputs to sense count values in each of five time interval ranges. These gates form the delay calculator. As the counter increments, the gates set flip-flops at specified counts which represent slice points between baud rates. When the next mark-to-space transition occurs, indicating the end of the select pulse, the flip-flops are sampled. The number of flip-flops which have been set determines the time between the space-to-mark and mark-to-space transitions, indicating (within the predetermined ranges) the select pulse duration. For example, when the counter has incremented enough times to indicate that the select pulse length is greater than 11.40 ms, the output of the first gate sets its associated flip-flop. A second gate sets

its flip-flop when the counter reaches a count corresponding to a time interval of 15.01 ms or greater. The remaining flip-flops are set in a similar manner if the count becomes high enough.

Four additional gates, one for each operating speed, comprise the baud calculator. These gates are used to determine whether the measured interval corresponds to the select pulse length for a particular operating speed. For example, if the first delay calculator flip-flop is set but the second is not, then the pulse duration is greater than 11.40 ms but less than 15.01 ms. The first of the baud calculator gates detects this condition. Since this time interval range corresponds to the select pulse duration for a 100 WPM signal, the 100 WPM lamp (a light-emitting diode, or LED) is lit. The other three baud calculator gates are inactive and their lights are left in the off state. The same principle applies for each of the other operating speeds. If no time flip-flops are set or all flip-flops are set, this indicates that the select pulse was either too small or too large and the previous state of the LED's is preserved. It should be noted that since select times are being measured, bias distortion on the signal may cause an incorrect indication.

#### MEMORY AND DISPLAY SECTION

The memory and display section stores the character codes supplied by the input section, converts each one to a pattern of dots to form the display, and generates a composite video signal to drive the monitor.

The system incorporates three different memories. The first is the page memory, into which the incoming characters are written. Each time a row of characters is to be displayed, forty characters are transferred from the page memory to the line memory, where they are stored temporarily and supplied, one at a time, to the character generator circuitry. A read-only memory in the character generator converts the ASCII codes to the pattern of dots needed for the display.

The remainder of the memory and display section consists of the master clock oscillator, the video timing generator and combiner, and various control circuits, as shown in the block diagram.

#### Master Clock Oscillator

All functions of the memory and display section are timed and synchronized by the crystal-controlled master oscillator shown in Figure 6.1. It operates at a frequency of 12.2727 MHz.

#### Page Memory and Control

The page memory stores all 1000 characters which make up a display "page" (25 lines of 40 characters each). Character codes in parallel format arriving from the input section enter the page memory; they are transferred in groups of 40 to the line memory, where they are used to generate one horizontal row of characters in the display.

The page memory consists of six 1,024-bit shift registers operating in parallel, as shown at the left in Figure 6.4. Since only 1000 characters are stored at any time, the extra 24 locations in each register are unused.

The display, which conforms to U.S. television standards, is recreated or "refreshed" 60 times per second. That is, 60 complete video fields per second are interlaced to produce 30 complete video frames. Both fields of a given frame contain the same information. The contents of the page memory are read out each time a new field is produced, once every 60th of a second.

To read out the memory, the shift registers are clocked by pulses derived from the master oscillator. The six bits for each successive character appear in parallel at the register outputs every time a clock pulse occurs. The readout process, however, must be nondestructive—the characters must be retained in the memory for use during subsequent video fields. A feedback path is provided so that characters read out are fed back to the inputs of the registers. At the same time that a character is read out to the line memory it is fed back to the page memory inputs (unless it belongs to a row which is to be deleted or is the one being written by the input section).

Although the memory contains 1,024 locations, only 1,000 are used. The extra 24 locations which are not used must be skipped over during each complete cycle of the memory. Therefore, 24 extra clock pulses are supplied to the memory by the retrace clock generator at the end of each video field during the vertical retrace interval. The memory cycle is then complete and the code for the first character is at the output end of the memory registers, ready to be clocked out again when the next video field starts.

The page memory control circuitry synchronizes the memory cycle with the production of each video field. When a row of characters is to be displayed, it passes 40 clock pulses to the page memory registers, causing 40 characters to be transferred to the line memory and also recycled to the page memory inputs. The memory is not clocked again until the complete row of characters has been produced, a process which requires nine video scan lines. Since there are 25 rows of characters per page, the clocking process is repeated 25 times for each video field.

#### Line Memory and Control

Nine horizontal scan lines are used to display each row of characters, as Figure 3.3 illustrates. The first line is left dark. The next seven contain the dot patterns which make up the characters, and the remaining one is again left dark. The dark lines separate the rows of characters from each other. The line memory cycles the stored characters while the nine lines are being scanned, feeding the characters in sequence to the character generator ROM at the proper time during each scan.

(a) Dot patterns for characters "A" and "3"

(b) Character generator output codes for scan line 2 of characters "A" and "3"

Figure 3.3 Typical Display Pattern

Six 40-bit shift registers comprise the line memory. As with the page memory, the six registers operate in parallel and are equipped with feedback loops for recycling the stored data. Since the line memory storage capacity is exactly equal to the number of characters to be stored, however, no end-correction circuit is required.

During the first scan line for a new row, the characters to be displayed are transferred from the page memory to the line memory by clocking both memories simultaneously. The character generator produces no output during this scan, so the previous characters stored in the line memory are clocked out without producing dots on the screen.

During each of the next seven scan lines, all 40 characters in the line memory are recycled and also fed to the character generator in succession. During the last line, which is left dark, the memory contents are recycled, but the character generator is again instructed to produce no output.

A control circuit passes clock pulses to the line memory shift registers on the *line clock* bus whenever characters are to be entered or recycled. The line address counter keeps track of the number of shift pulses supplied to the registers. It cycles from zero through 39 as a complete row is transferred from the page memory to the line memory during the first scan line of a row. It also completes a cycle for each of the other eight scan lines needed to produce a row of characters. It therefore records which of the 40 characters in a row is being transferred at a particular instant. Every time this counter recycles, it increments the scan line counter, which keeps track of the scan

line number. The control circuit breaks the line memory feedback loop during the first scan line when character data are being entered from the page memory. The scan line counter outputs are fed to the character generator as part of the address code which determines the position of dots on the screen. Each complete cycle of the scan line counter causes the page address counter to increment. Hence, the latter counter increments each time a complete row of characters is displayed, and it therefore records the number of the row being produced.

#### Character Generator

The character generator is a read-only memory custom precoded to store the dot patterns for 64 different characters. When supplied with the proper input address codes, the memory outputs a digital code corresponding to the dot pattern required for each character.

Since every character is produced by seven scan lines, the dot pattern in each line may be different, as shown in Figure 3.3a. The character ROM must therefore be instructed not only what character to produce, but what scan line of that character is being generated. The character codes come in sequence from the line memory; the scan line number is supplied by the scan line counter in the line memory control circuit.

The characters are five dots wide. The ROM therefore provides five output bits, one for each dot. If a given bit is a "1", a dot is produced on the screen; if the bit is a "0", the space is left dark, as Figure 3.3b illustrates.

The first scan line is left dark by instructing the character generator to display line number zero. All character locations in the character ROM for this scan line are left blank, so no output results regardless of the input data coming from the line memory. During the second scan line, the line memory again cycles and all 40 characters for the row being produced are fed to the character ROM in sequence, along with the scan line number. As the character codes are fed in, the dot codes for the characters appear at the character ROM output.

When the scan line is complete, the scan line counter again increments, the memory is again cycled through all 40 characters, and the character ROM produces the dot pattern for the third scan line. This process is repeated until the eighth scan line is complete. During the ninth scan line, the character ROM is again instructed to produce line zero. No video output results, and the last line is therefore dark.

#### Cursor Generator

The flashing cursor, which indicates the position of the next character to be entered in the display, is produced by instructing the character ROM to produce the cursor symbol in the position immediately following the last character entered in the bottom row of the display. The cursor logic senses the state of the input character counter and drives the chip enable input of the character ROM at the desired instant during the line memory cycle as the characters in the 25th row of the display are being supplied to the character ROM. Disabling the ROM causes its outputs to go high, resulting in a white line

The cursor is made to flash by an oscillator which alternately enables and disables the cursor logic.

#### Data Entry Control

Characters supplied from the input section must be transferred to the page memory at the correct instant in its cycle if they are to appear at the proper position on the screen. A character which has been received, assembled, and converted in the input section is stored there momentarily until the page memory is ready to accept it. The write logic synchronizes the transfer of the character to the page memory.

Character codes are transferred to the page memory just previous to the production of the bottom (25th) row of characters on the screen. The transfer occurs during the first (blank) scan line of that row, when the page memory contents for the 25th row are being entered in the line memory.

An input character counter keeps track of the number of characters which have been entered from the input section. As with the line address counter, it cycles from 0 through 39. It is reset to zero at the beginning of each new row. At that point in the operating cycle when (1) the page address counter reads 24, indicating that the last (25th) row of characters is being produced, (2) the scan line counter reads 0, indicating that the first scan line of the row is being generated, (3) the line address counter contains the same number as the input character counter, and (4) the character write flip-flop indicates that a converted character is waiting in the input section, the transfer occurs. New characters therefore always appear in the bottom line of the display.

The new character is read into the page memory by breaking the feedback path of the memory shift register when the input character counter and the line address counter coincide. The previously stored character (a space) is therefore not fed back to the page memory input on the next shift pulse. The new character is entered in its place. The feedback path is then reestablished before the next shift pulse occurs.

To illustrate this process, let us assume that the screen is filled except for the last line, and that nine characters have already been written in that line. A new character is assembled in the input section and the character write flip-flop is set. The input character counter contains the number nine, indicating that nine characters have already been entered in the row and that the new one will be the tenth. When the character has been entered, the counter is advanced to 10.

As the page memory starts through its cycle, the line address and page address counters increment. When the page address counter reaches 24, indicating that the last line is being read out, and the line address counter reads nine, showing that the first nine characters in the last row have been read out, the feedback path is broken, the next stored character is deleted, and the new one is entered in its place. The feedback path is then reconnected, and the memory continues through its cycle. The next new character will be entered in the same manner on a later memory cycle.

Since the page memory completes a cycle every 16.7 ms, the delay while the converted character in the input section awaits transfer to the page memory is short compared to the time it takes to assemble the next incoming character (about 100 ms at 100 WPM).

#### Line Feed Control

A line feed command can originate from any of three sources: (1) the control code detector in the input section whenever a line feed code is received or when a space is received after the 34th character in a line, (2) the page address and line address counters when they recycle, indicating that the last line of the display has been filled, and (3) the manual line feed pushbutton. The line feed logic circuit detects any of these conditions.

When a line feed request signal has been produced by one of these sources and when the various counters indicate that the last scan line of the character display is complete, the page memory feedback path is broken and the memory is clocked an extra 40 times. The 40 characters which would otherwise have constituted the first row of the next display field are clocked out of the memory. Since the feedback path is broken, these characters are lost. Space characters are supplied to the register inputs during this clocking operation so that the last line of the next display field will be blank. All other characters are moved up one line in the process.

Whenever a line feed occurs, the input character counter is reset to zero. Consequently the next new character is written at the leftmost position of the bottom line. In this way, a carriage return is automatically produced with each line feed, regardless of how the line feed command originated.

#### Output Shift Register

As the line memory cycles, the five dot code bits for each character appear in parallel at the character ROM output. To produce dots at the proper time (and hence the proper position on the scan lines), the dot code bits must be fed serially to the video output circuits. A five-bit shift register performs the parallel-to-serial conversion.

Upon a command from the line memory control, the character ROM output bits are loaded into the shift register. They are then clocked out of the register into the video combiner by pulses from the master clock. After all five bits have been transferred and before the register is reloaded with the dot code for the next character, two extra clock pulses are allowed to pass. These extra pulses result in a blank space two dots wide between characters.

#### Video Circuitry

The dot code which comes from the character generator via the output shift register must be mixed with video synchronization and blanking signals and fed to the external monitor. The video circuits perform these functions.

A special IC contains all the circuitry needed to produce the video synchronization and blanking pulses. Its input is driven at 2.0475 MHz by a scaler which divides the master oscillator frequency by a factor of six.

The sync generator outputs are shown in Figure 3.4. One horizontal sync pulse and one horizontal blanking pulse are produced for each of the 525 lines in a video frame. One vertical blanking pulse is produced for each of the 60 fields scanned every second. Since standard television format uses interlace scanning, the blanking signals for alternate fields are offset from each other by one-half of a horizontal scan time. The sync generator outputs are fed to the video combiner as well as to the horizontal and vertical position controls, where they are used to position the display in the center of the screen.

The video combiner mixes the video, blanking, and synchronization signals and drives the external video monitor. The combiner is composed of three switched constant current sources, each of which is driven by one of the three input signals. The video monitor input impedance serves as a common load for all three current sources, so the output to the monitor is the sum of the three input signals. Figure 1.4 shows the composite video waveform.

Figure 3.4 Video Timing Signals

#### 4. Maintenance

Your RVD-1005 has been carefully engineered and is constructed from high-quality components to ensure years of troublefree service when installed and operated properly. The unit requires no routine maintenance, and in current production models there are no internal adjustments. On models with serial numbers less than 241, a control is included to adjust the +5 volt output voltage of the regulated power supply. The setting of this control will not need to be changed under normal circumstances but should be checked in case the unit malfunctions. The procedure is explained below.

#### In Case of Difficulty . . .

Because the logic circuitry of the RVD-1005 is quite complex, extensive troubleshooting should be done only by an experienced technician who is familiar with high-speed digital logic circuitry and who has the proper test equipment, including a wideband, triggered-sweep high-performance oscilloscope, at his disposal. Please note that the warranty is void if repairs are attempted by an unauthorized person.

If the unit fails to operate properly, it is usually most satisfactory to return it to HAL Communications Corp. for repair after making the basic tests described below. If you plan to send your unit in for factory service, please notify the company by telephone or letter and wait to ship it until you receive a return authorization card.

#### Basic Troubleshooting

Before opening the cabinet to make internal measurements, make the following checks:

- Be sure that the line cord is connected to an AC power source of the correct voltage and frequency. Units designed for 220 V AC operation are identified by a tag on the rear panel or the line cord.

- 2. Check the fuse in the holder on the rear panel.

- 3. Reread the operating instructions in Section 2 to make certain that you are using the unit correctly.

- 4. Reinspect the connections to the input signal source (RTTY loop circuit or demodulator) and to the video monitor.

- Check the input signal from the loop or demodulator with an oscilloscope or by feeding it to another printer system and

observing whether that system performs properly. Be sure to determine whether the voltage or current levels fall within the range specified in Section 1.

6. Test the monitor, if possible, by disconnecting the feed cable from the visual display unit and driving the monitor with a test signal.

If these checks do not reveal the source of the problem, a few internal tests may be made if the appropriate test equipment is available:

- Remove the top cover. CAUTION: High voltages are exposed when the cover is removed. Make the following measurements with great care. To prevent possible injury or damage to the unit, be certain that the test probe does not short between adjacent connections or conductors.

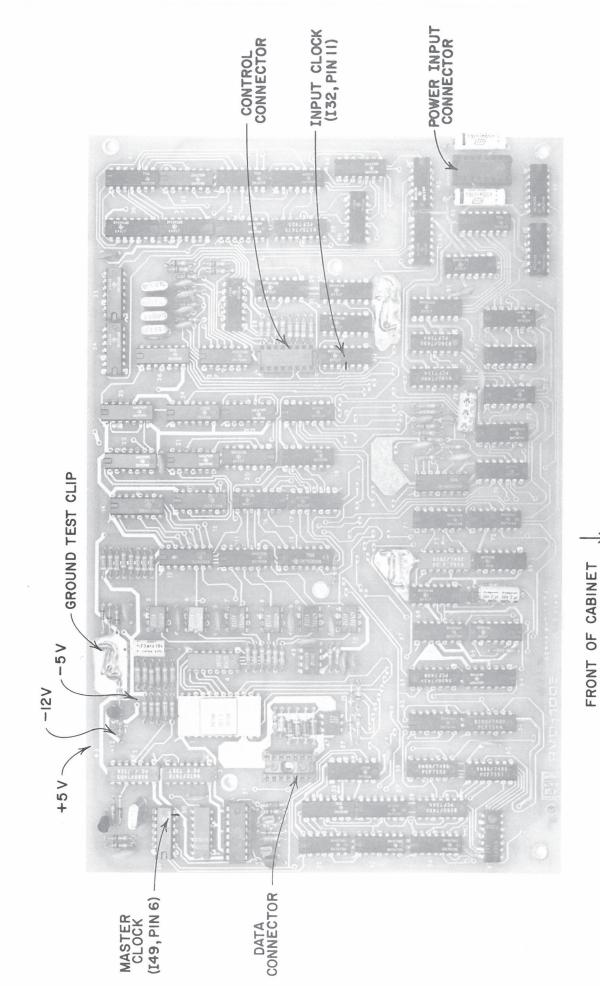

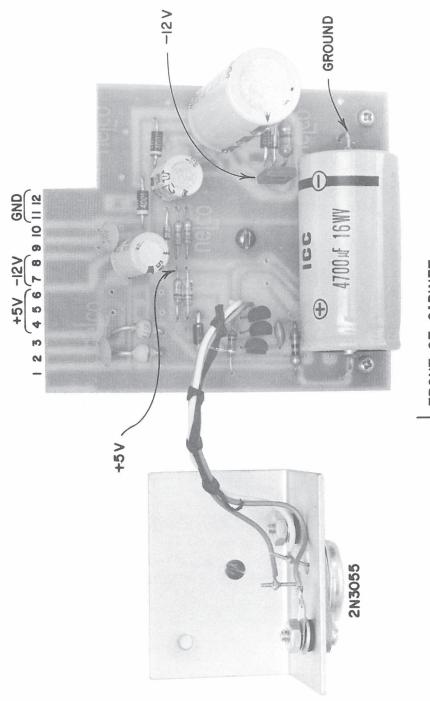

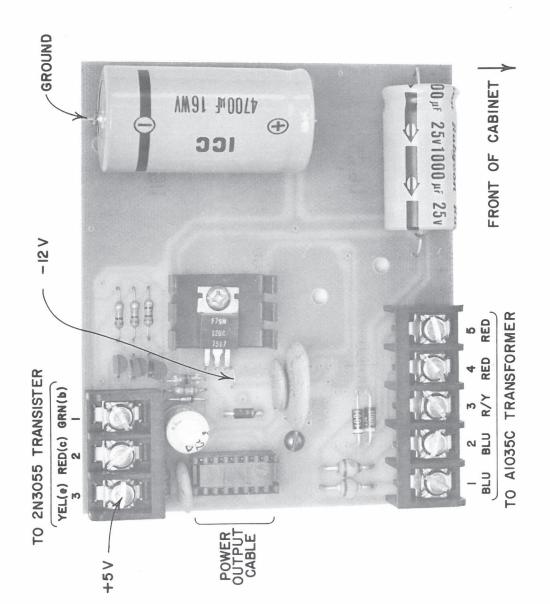

- 2. Switch the unit on. Ground the negative lead of an accurate  $(\pm 3\%)$  voltmeter to the cabinet and measure the voltages present at each of the points listed in Table 4.1. The test points are shown in Figures 7.1, 7.2, and 7.3.

Table 4.1

Voltage Measurements

| Parameter | Measurement Point                         | Acceptable Range     |

|-----------|-------------------------------------------|----------------------|

| +5 volts  | Power Supply Board<br>Logic Circuit Board | +4.9 to +5.2 volts   |

| -5 volts  | Logic Circuit Board                       | -4.9 to -5.7 volts   |

| -12 volts | Power Supply Board<br>Logic Circuit Board | -12.0 to -12.2 volts |

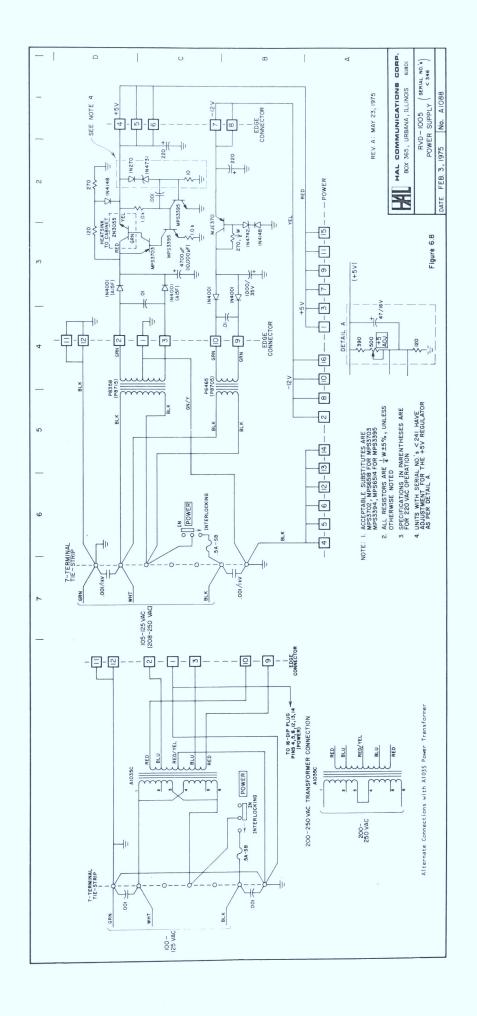

Early models of the RVD-1005 used a power supply circuit board with a potentiometer for adjustment of the +5 volt power supply. This potentiometer (the only potentiometer on the power supply board) should be set for a +5.0 volt output as measured on the logic circuit board. The circuit of this model of the power supply is detailed in Figure 6.8, detail A.

Units with serial numbers higher than 241 use power supplies with fixed voltage outputs. If voltages are measured that are not within the indicated acceptable range, first check the accuracy of the voltmeter. If the problem persists, the probable cause is a short, defective component, or overload. Check for overload by turning

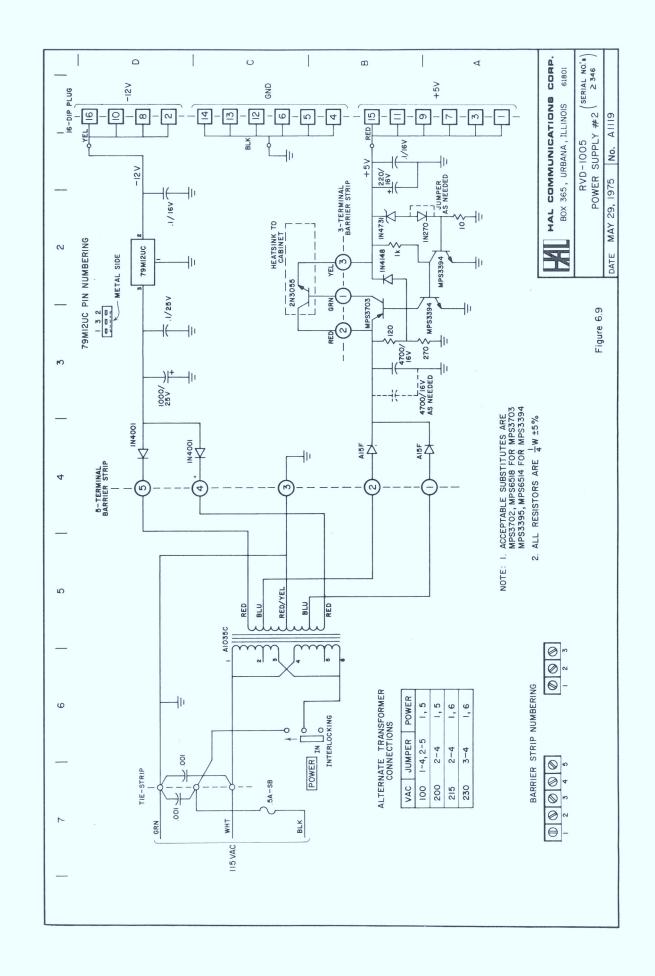

the RVD-1005 off, disconnecting the power cable to the logic board, and re-measuring the voltages at the power supply with the logic board disconnected. All voltages may measure as much as 10% higher with the logic board disconnected. Note that the -5 volts is derived on the logic board from the -12 volt supply and will therefore not be found on the power supply board. The three versions of power supplies that have been supplied with the RVD-1005 are diagrammed in Figures 6.8 and 6.9. Models with serial numbers less than 241 use the supply of Figure 6.8, detail A; serial numbers between 241 and 345 use the supply of Figure 6.8 and 7.2; serial numbers higher than 345 use the circuit board shown in Figure 6.8 and 7.3.

3. If the voltages are correct, the operation of the internal oscillators may be checked by observing their output waveforms with an oscilloscope having a vertical bandwidth of 10 MHz or greater. Check for the presence of output from the input clock oscillators at the point labelled INPUT CLOCK in Figure 7.1. Check each of the four oscillators in turn (one for each operating speed) by depressing the speed selector switches in succession and looking for the presence of a waveform on the oscilloscope. The frequencies should be in the range from 5.9 to 9.7 MHz. The exact frequencies are listed in Section 3, Table 3.2.

Check the master clock oscillator by connecting the oscilloscope probe to the point labelled MASTER CLOCK in Figure 7.1. A 6.1425 MP-signal should be present. This signal is derived from a 12.2727 MH crystal oscillator through a divide-by-two circuit.

If any of these signals is not present, check the oscillator circuitry. A schematic of the input timing oscillators is shown in Section 6, Figure 6.6, and the master clock is shown at the right in Figure 6.1.

Problems not isolated by these simple tests should normally be referred to the factory. Further information on the operating principles of the circuitry is given in Section 3. A complete set of schematic diagrams is included in Section 6.

### 5. Using a Television Set as a Monitor

Most standard American television sets can be easily modified to serve as video monitors. The change does not affect normal operation of the set except that the cable should be removed from the TV set for normal viewing.

CAUTION: Do not attempt to use as a monitor any television receiver in which one side of the AC line is connected to the chassis or circuit ground unless you supply AC power to the set from a reliable isolation transformer.

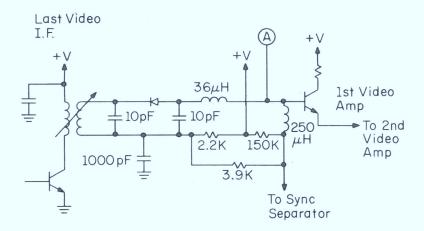

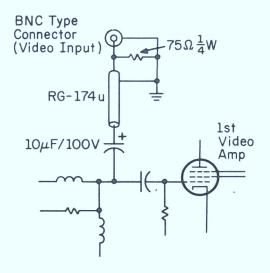

The modification is simply a matter of capacitively coupling the external video signal to the input of the first video amplifier stage. Figure 5.1 shows a typical transistorized video circuit. Although the component values and the biasing method may be slightly different in your set, the circuit will be essentially as shown. The video signal is injected at point A.

Figure 5.1 Typical Transistor Video Detector

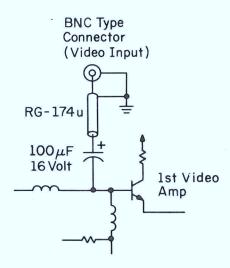

The modified circuit is shown in Figure 5.2. Connect the negative end of a 100  $\mu$ fd, 16 volt electrolytic capacitor to the base of the first video amplifier transistor. Mount a BNC connector on the cabinet as close as possible to the transistor. Using a short length of hookup wire, connect the center pin of the BNC connector to the positive end of the capacitor. If the distance is short, the capacitor leads themselves may take the place of the hookup wire. On the other hand, if the distance is greater than six inches,

substitute a length of coaxial cable. Miniature coax, such as RG-174/U, may be used even though its characteristic impedance is 50 ohms.

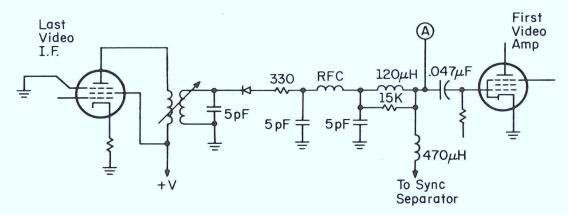

Figure 5.3 shows a typical video circuit using tubes. The external video signal is injected at point A. Connect the negative end of a 10  $\mu fd$ , 100 volt electrolytic capacitor to the detector side of the existing coupling capacitor, as shown in Figure 5.4. Note that a 75 ohm resistor is wired across the input connector to provide the proper load impedance for the RVD-1005 output.

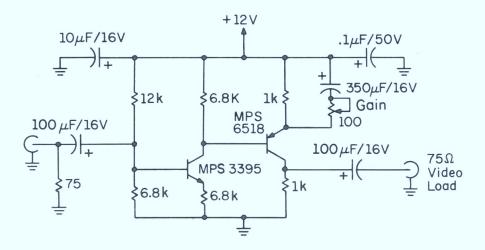

Some tube-type sets may require a video level of 3 volts peak-to-peak to provide good contrast. In that case a two-stage video amplifier, such as that shown in Figure 5.5, may be inserted in the line from visual display system to the television set.

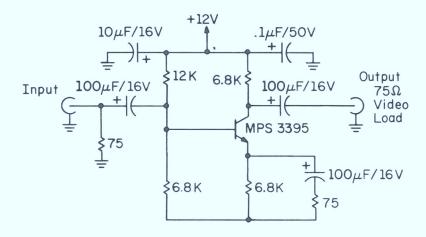

In some sets the video at the coupling point may have reverse polarity, with positive-going synchronization pulses and negative video information. This situation will often be found in transistorized sets which use a negative power supply and PNP transistors. The unity-gain phase inverter shown in Figure 5.6 may be inserted in the line from the RVD-1005 to reverse the video signal polarity.

Figure 5.2 Modified Transistor Video Detector

Figure 5.3 Typical Tube-type Video Detector

Figure 5.4 Modified Tube-type Video Detector

Figure 5.5 Video Amplifier

Figure 5.6 Video Inverter

## 6. Schematic Diagrams

In this section you will find the schematic diagrams for the RVD-1005, as listed below. The drawing conventions are depicted in Figure 6.10.

```

Figure 6.1:

Video, Line Feed, and Retrace Control

Figure 6.2:

Page Position Control

Figure 6.3:

Line Position Control

Figure 6.4:

Character Memory

Figure 6.5: Input Control Decode

Figure 6.6: Input Timing Chain

Figure 6.7:

Baud Rate Estimator

Figure 6.8:

Power Supply (serial numbers less than 345)

Power Supply (serial numbers 346 and higher)

Figure 6.9:

```

## 7. Printed Circuit Card Layouts

The following photographs show the position of components on the printed circuit cards as well as typical cabinet interior details. Some late model changes may not be shown in these photographs.

Figure 7.1 Logic Circuit Board Photograph

FRONT OF CABINET

Figure 7.2 Power Supply (Serial No. less than 345)

Figure 7.3 Power Supply (Serial No. 346 and higher)

Figure 7.4 Interior of RVD (Serial No. less than 345)

Figure 7.5 Interior of RVD (Serial No. 346 and higher)

## 8. Parts List

| Int                                                                                                        | egrated Circuits                                                                                                                                                                                      | Cry                                                   | stals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Misc                                                                                                            | cellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1<br>6<br>1<br>1<br>7<br>1<br>7<br>7<br>1<br>1<br>9<br>9<br>1<br>2<br>4<br>2<br>1<br>1<br>1<br>1<br>1 | FCD 810 2513N / CM9350 MM5013N (or 2525V) MH0026CN MM5320N 2519B 7400 7402 7404 7405 7410 7420 7430 7472 7473 7474 7475 7486 7490 7492 7493 7495 74123 74174 74188AN (red) 74188AN (blue) 74504 79M12 | 1 1 1 1 1 1 1 1 2 2 5 1 6 1 1 1 4 1 3 1 8 1 2 2 6 1 1 | 5957.81 kHz 6553.60 kHz 7459.98 kHz 9730.66 kHz 12272.7 kHz  istors  2.2 ohm, ¼ watt 10 ohm, ¼ watt 82 ohm, ¼ watt 120 ohm, ¼ watt 150 ohm, ¼ watt 120 ohm, ¼ watt 150 ohm, ¼ watt 120 ohm, ¼ watt 120 ohm, ¼ watt 150 ohm, ¼ watt 220 ohm, ¼ watt 330 ohm, ¼ watt 270 ohm, ¼ watt 4.7K ohm, ¼ watt 1.2K ohm, ¼ watt 1.2K ohm, ¼ watt 2.ZK ohm, ¼ watt 4.7K ohm, ¼ watt 4.7K ohm, ¼ watt 1.0K ohm, ¼ watt | 1<br>1<br>3<br>1<br>1<br>1<br>1<br>1<br>2<br>4<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | D1106 Circuit Board D1024 Circuit Board 16 DIP Sockets 14 DIP Socket 14 DIP Plug 16 DIP Plug 16 DIP Plug w. cable UG1094 Connector 0309-2061 Connector 0309-1061 Connector 0209-2143 Male Pins 0209-1143 Female Pins Video Cable w. connectors 3 lug terminal strips 3 lug barrier strip 5 lug barrier strip 6107B14 Heat Sink Heat Sink for 2N3055 A1035 Power Transformer 8 Position PB Switch Power Cord HKP Fuse Holder ½ amp. SB Fuse ½" Plastic Stand-offs 6-32 x ½" Metal Spacers Strain Relief Cabinet with Hardware RVD-1005 Manual |

| Transistors                                                                                                |                                                                                                                                                                                                       | Capacitors                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |